About Me

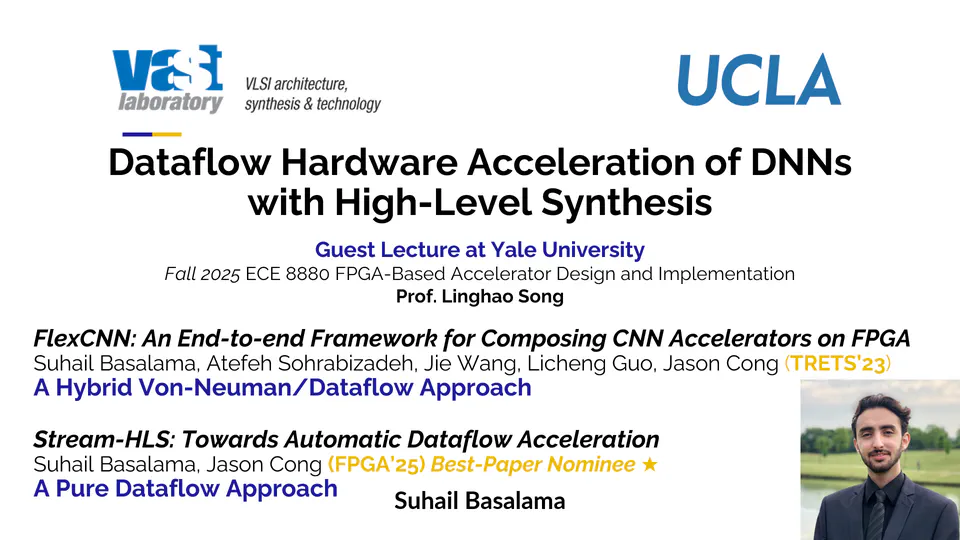

Suhail Basalama is a Ph.D. student in Computer Science at the University of California, Los Angeles, working in the VLSI Architecture, Synthesis, and Technology (VAST) Lab. His research focuses on hardware acceleration for machine learning, custom and domain-specific computing, and high-level synthesis. He has developed novel methodologies, compilers, and frameworks for optimizing systolic arrays, spacial accelerators, and dataflow architectures.

- ML/AI software-hardware co-design

- Compiler construction for HW accelerators

- Systolic, and dataflow architectures

- Design-space exploration methodologies

- Performance and system modeling

- Hardware compilation and synthesis

- Domain-specific and customized computing

- EDA and VLSI design methodologies

Ph.D. in Computer Science

University of California, Los Angeles

M.S. in Computer Science

University of California, Los Angeles

B.S. in Computer Engineering

University of Arkansas

B.A. in Political Science

University of Arkansas

I’m a Ph.D. researcher at UCLA’s VAST Lab, working at the intersection of hardware and machine learning. My work spans hardware-software co-design, high-level synthesis, and efficient accelerator architectures for ML workloads. I build hardware compilers, frameworks, and design space exploration tools for automating ML hardware acceleration on FPGAs and ASICs.

Always happy to discuss research, exchange ideas, or collaborate! 😊